# Program Logic

# Version 8.1

# IBM System/360 Time Sharing System Resident Supervisor

Describes the internal logic of the resident supervisor, and provides a brief overview of its operation. It is intended as a reference for anyone involved in maintaining or altering resident supervisor logic.

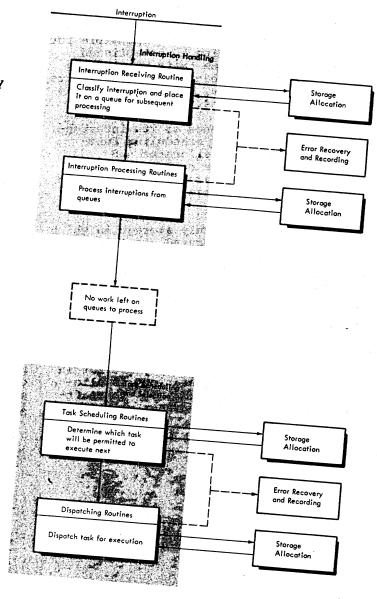

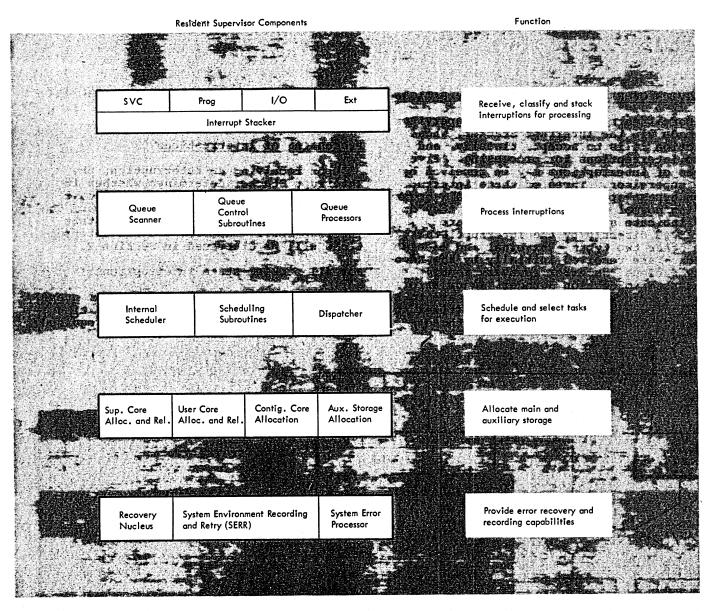

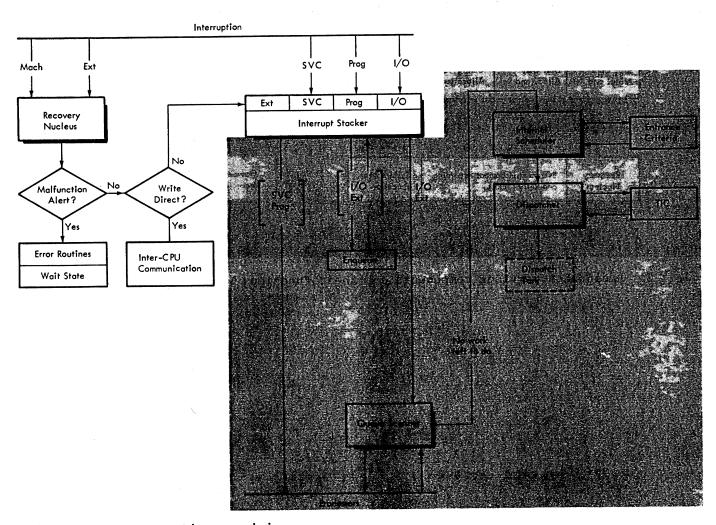

The resident supervisor schedules and dispatches tasks, provides services that might endanger system integrity if a task were allowed to execute them, handles interruptions, and deals with system errors. It is permanently resident in main storage.

The first and second sections of the book are intended to introduce the reader to the functions of the resident supervisor, and to provide him with an easily used, overall presentation of resident supervisor logic. Interruption handling is described from the point at which the interruption occurs until it has been completely processed. Paging and queuing are discussed. The third and fourth sections describe in some detail the individual modules that make up the resident supervisor. These modules are discussed under the following headings: interruption classification, queue scanning and processing, storage allocation, SVC processing, paging, I/O handling, task selection and scheduling, and error recovery. The appendixes contain module IDs and names of supervisor routines, and SVC codes.

The prerequisites for this publication are: <a href="IBM\_system/360">IBM\_system/360</a> Principles of Operation, GA22-6821, and <a href="IBM\_system/360">IBM\_system/360</a> Time Sharing System: Concepts and Facilities, GC28-2003.

This publication describes the logic and operation of the TSS/360 resident supervisor. It is divided into four sections and two appendixes. Section 1, the introduction, describes the purpose and major components of the resident supervisor, and how these compenents interact with the rest of Section 2, the method of opera-TSS/360. tion, describes resident supervisor interruption handling, queue processing, storage allocation, and task selection and scheduling. Section 3, program organization, discusses the internal logic of the resident supervisor. Each routine is described in detail. Section 4 contains flowcharts for the more complex supervisor modules. Appendix A contains a list of module IDs and entry point names for all modules in the resident supervisor. Appendix B is a table of defined SVC codes and their meaning.

This publication is intended for use by anyone involved in maintaining or altering

resident supervisor logic. It will be particularly useful to systems programmers.

# PREREQUISITE PUBLICATIONS

Familiarity with the material contained in the following publications is essential to the use of this manual:

IBM System/360 Principles of Operation,

GA22-6821

IBM System/360 Time Sharing System: Concepts and Facilities, GC28-2003

In addition, <u>IBM System/360 Time Sharing</u>

System: System Control Blocks PLM, GY282011, and <u>IBM System/360 Time Sharing System: Assembler User Macro Instructions</u>,

GC28-2004, should be available for reference purposes.

# Sixth Edition (September 1971)

This is a major revision of, and makes obsolete, GY28-2012-4.

This edition reflects changes to the resident supervisor intended to improve its performance and make it even more efficient. Several task selection and scheduling methods have been changed, the paying error recovery function has been expanded, and XTSI paging has been revised. In addition, the structure of the book itself has been changed for easier reference and a method of operation section added.

This edition is current with Version 8, Modification 1, and remains in effect for all subsequent versions or modifications of IBM System/360 Time Sharing System unless otherwise indicated. Significant changes or additions to this publication will be provided in new editions or Technical Newsletters. Before using this publication, refer to the latest edition of IBM System/360 Time Sharing System: Addendum, GC28-2043, which may contain information pertinent to the topics covered in this edition. The Addendum also lists the editions of all TSS/360 publications that are applicable and current.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 printer using a special print chain.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form is provided at the back of the publication for reader's comments. If the form has been removed, comments may be addressed to the IBM Corporation, Time Sharing System/360 Programming Publications, Department 643, Neighborhood Road, Kingston, New York 12401

© Copyright International Business Machines Corporation 1967, 1968, 1969, 1970, 1971

# CONTENTS

| SECTION 1. INTRODUCTION                                           | 1    |

|-------------------------------------------------------------------|------|

| Relationship to the System                                        | 1    |

| Purpose and Functions                                             | 1    |

| Major Components of the Resident Supervisor                       | 2    |

| im jor components of the execution of                             |      |

| CECTION 2 METHOD OF ODERATION                                     | 4    |

| SECTION 2. METHOD OF OPERATION                                    | 4    |

| Overview of Resident Supervisor Operations                        | 4    |

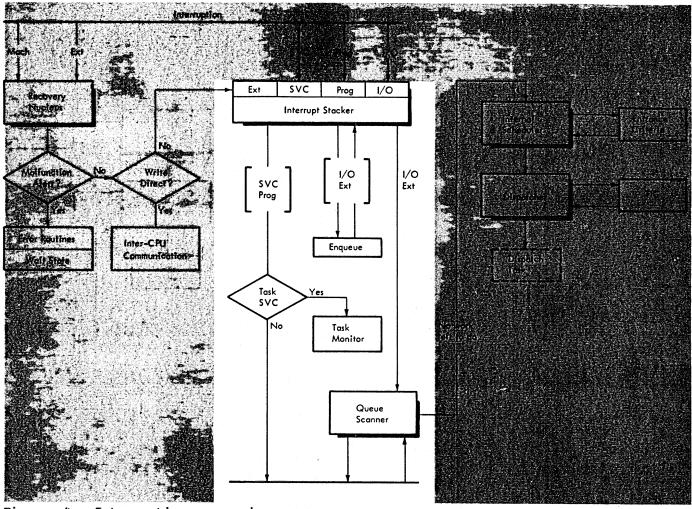

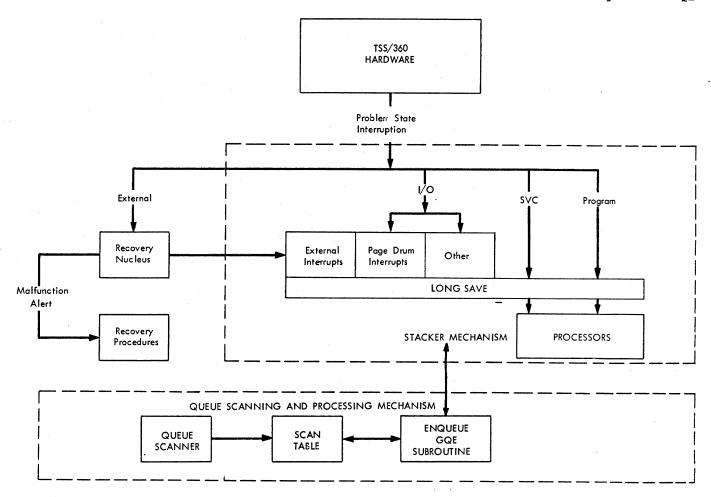

| Processing of Interruptions                                       | - 4  |

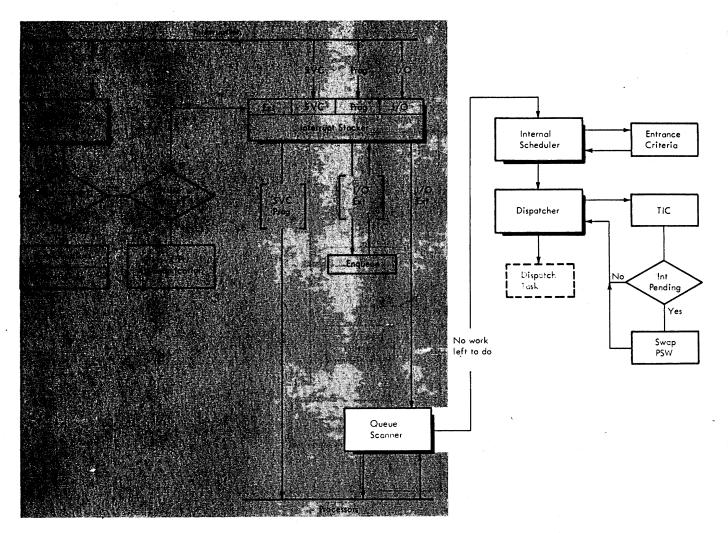

| Scheduling of Tasks                                               | 5    |

| Control Blocks Used by the Supervisor                             | 5    |

| Interruption Handling                                             | 6    |

| Entry to the Supervisor                                           | 6    |

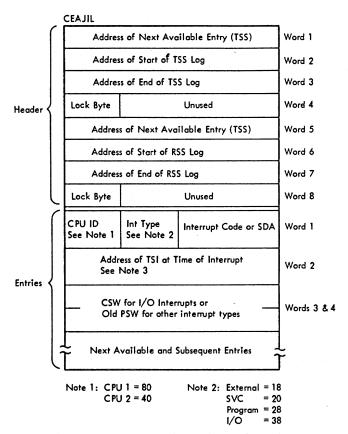

| General Oueue Entry (GOE)                                         | - 7  |

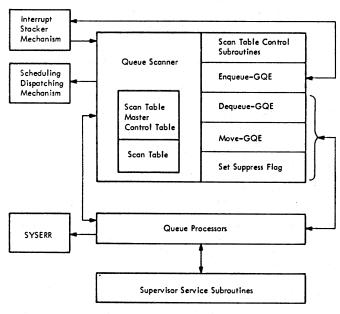

| Queue Scanning                                                    | 8    |

| Scan Table (SCANT)                                                | 8    |

| Scan Table Master Control Table (SMC)                             | Ω    |

| Scan lable Mastel Control lable (SMC)                             | 0    |

| Queue Scanner Functions                                           | 0    |

| Queue Processing                                                  | 9    |

| Timer Interruption Processing                                     | 9    |

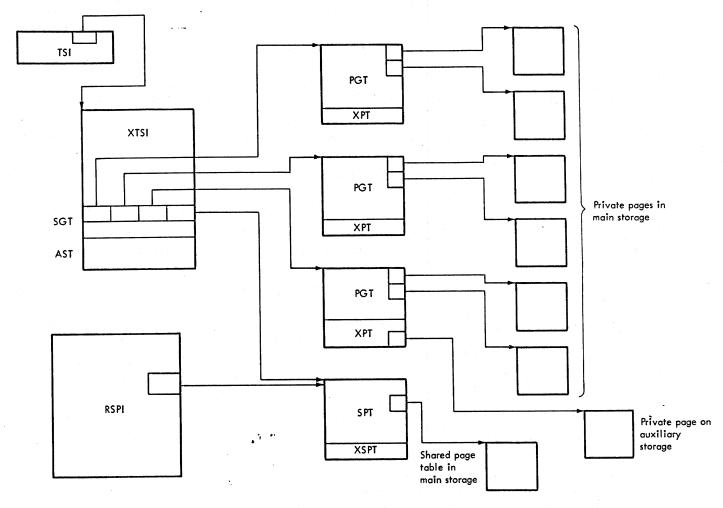

| Segment and Page Tables                                           | 10   |

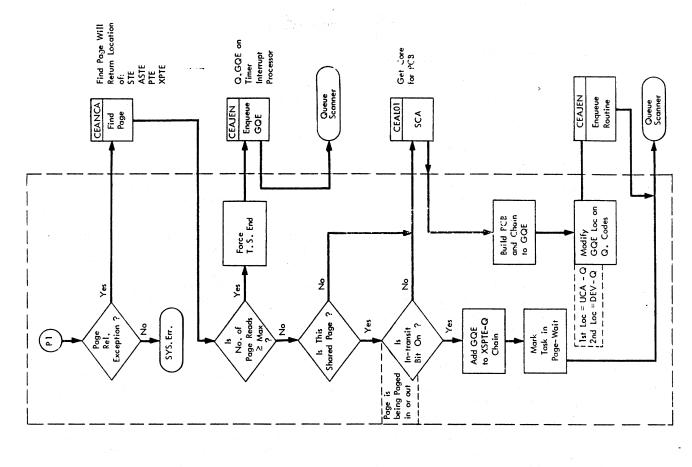

| Program Interruption Processing                                   | 10   |

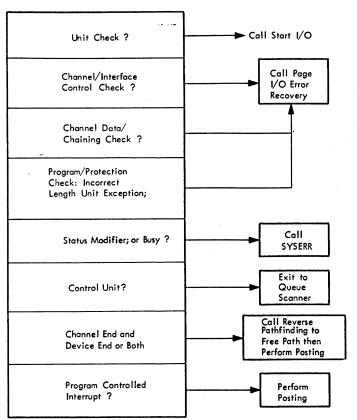

| I/O Interruption Processing                                       | 11   |

| I/O Interruption Processing                                       | 12   |

| Paging                                                            | 12   |

| raging                                                            | 12   |

| Disk Paging                                                       | 13   |

| Drum Paging                                                       | 13   |

| Main Storage Allocation                                           | 13   |

| User Core Allocation                                              | 14   |

| Supervisor Core Allocation                                        | 14   |

| Auxiliary Storage Allocation                                      | 15   |

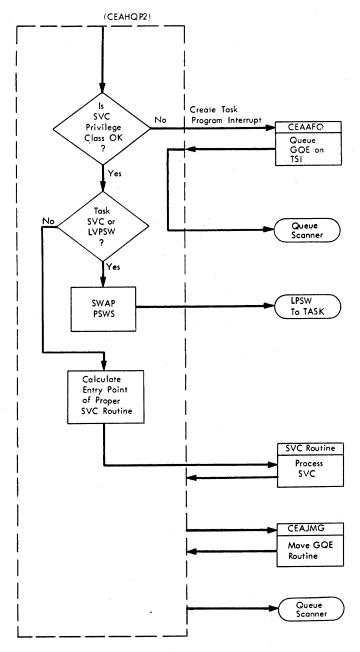

| SVC Interruption Processing                                       | 15   |

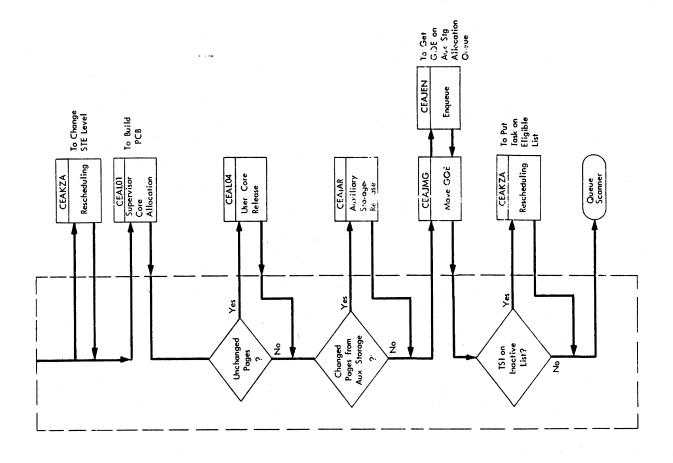

| Task Scheduling and Selection                                     | 16   |

| Schedule Table (CHASTE)                                           | 1.6  |

| Active and Inactive Lists                                         | 16   |

| Active and inactive Lists                                         | 10   |

| Task Selection                                                    | 1/   |

| Task Scheduling                                                   | 1/   |

|                                                                   |      |

| SECTION 3: PROGRAM ORGANIZATION                                   | 20   |

| Interruption Classification                                       | 20   |

| Interruption Classification                                       | 20   |

| Queue Scanner (CEAJQ) Chart AB                                    | 25   |

| (Would Sanner (CRIO) Chart AR                                     | 25   |

| Queue-Control Subroutines                                         | 24   |

| Queue-Control Subroutines                                         | 20   |

| Enqueue GQE Subroutine (CEAJQ Entered at CEAJEN)                  | 20   |

| Dequeue GQE Subroutine (CEAJQ Entered at CEAJDE)                  | 27   |

| Move GQE Subroutine (CEAJQ Entered at CEAJMG)                     | 28   |

| Set Suppress Flag Subroutine (CEAJQ Entered at CEAJSF) Chart AC . | . 28 |

| Queue Processors                                                  | 29   |

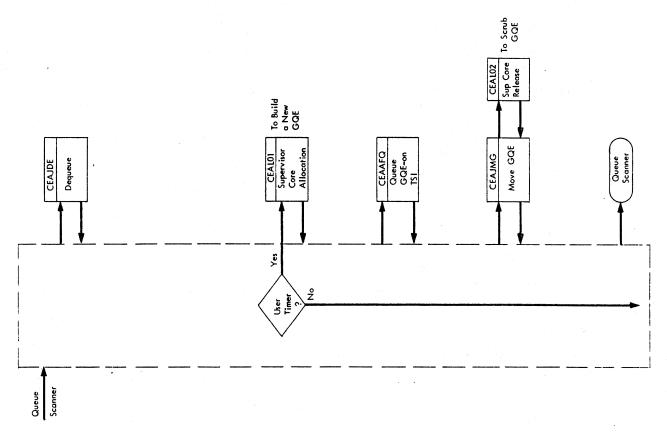

| Timer Interrupt Queue Processor (CEAKT) Chart AD                  | 29   |

| Page Drum Queue Processor (CEAA8) Chart AE                        | 33   |

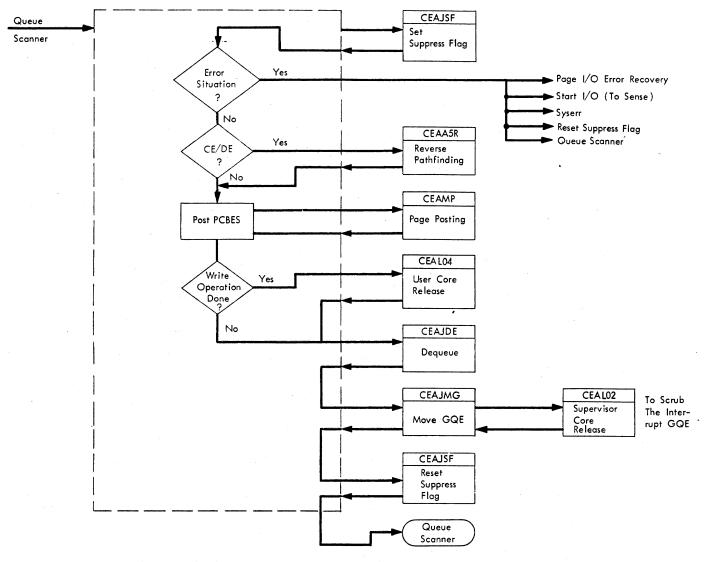

| Page Drum Interrupt Queue Processor (CEAA9) Chart AF              | 31   |

|                                                                   | 38   |

|                                                                   |      |

| I/O Device Queue Processor (CEAA3) Chart AH                       | 41   |

| Page Direct Access Interrupt Subprocessor (CEAA7) Chart AK        |      |

|                                                                   | . 45 |

| Channel Interrupt Queue Processor (CEAA4) Chart AK                | 47   |

| Remote Job Entry Asynchronous I/O Interrupt Subroutine (CEABA)    |      |

| Chart AL                                                          | 5:   |

| Remote Job Entry Synchronous I/O Error Interrupt Subroutine       |      |

| (CEABB)                                                           | . 50 |

| Terminal Communications Subprocessor (CEATC) Chart AM             | 51   |

| Storage Allocation Processors                                     | , J. |

| prorade withorarion brokespore                                    | , υ. |

|     | User Core Allocation Queue Processor (CEANB) Chart AN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 63         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|

|     | Auxiliary Storage Allocation Queue Processor (CEAIA) Chart AO .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 65         |

|     | Contiguous Core Allocation Queue Processor (CEANF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _   | 67         |

|     | Contiguous Core Allocation Queue Plocesson (CENT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •   | • •        |

|     | Supervisor Core Allocation Subroutine (CEAL1 Entered at CEAL01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |            |

|     | Chart AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •   | 69         |

|     | Supervisor Core Release Subroutine (CEAL1 Entered at CEAL02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |            |

|     | Chart AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •   | <b>7</b> 0 |

|     | Chart AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 71         |

|     | Auxiliary Storage Release Subroutine (CEAIA) Chart AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 71         |

|     | Auxiliary Storage Release Subroutine (CLAIR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •   | 72         |

|     | Suppress Auxiliary Allocation Subroutine (CEAAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •   | 72         |

| SVC | Owene Drogoggor and Service Routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •   | 12         |

|     | Cuparticar Call Onene Processor (CEAHO) Chart AU · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •   | 12         |

|     | Add nows subroutine (CFAHO entered at CEAHOA) Chart AK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •   | 73         |

|     | Add Shared Pages Subroutine (CEAQ6) Chart AS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 75         |

|     | Add Shared Pages Subjourne (Chago, Chare in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -   | 76         |

|     | Delete Page Subroutine (CEAND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •   | 77         |

|     | Set External Page Table Entries Subroutine (CEAH7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •   | 70         |

|     | wass Bottomal Dago Wable Entries Subroutine (CEAPU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •   | 10         |

|     | Commont to Chared Dage Table Subroutine (CEAU// Chait A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Τ.  | 78         |

|     | - Discours Commont From Shared Page Table Subroutine (CLAVO) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •   | 17         |

|     | Check Protection Class Subroutine (CEAQ4) Chart AU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ٠.  | 79         |

|     | Check Protection Class Subjustine (Chigy, Chartering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _   | 80         |

|     | Create-TSI Subroutine (CEAMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •   | 90         |

|     | Special Create TSI Processor (CEAT2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •   | 00         |

|     | Delete MCI Progossor (CFAMD) Chart AV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •   | 00         |

|     | - alt vmct Diold Cubrourine Hrabal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •   | -          |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _   | n ı        |

|     | Extract TSI Field Subroutine (CEAH2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 82         |

|     | Extract XTSI Field Subroutine (CEAS4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _   | 82         |

|     | Extract XTS1 Field Subroutine (CEAST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ī   | 83         |